更好的边缘缺陷测量能够提高良率,同时防止晶圆破损,但可能出现的缺陷数量正在增加。

随着开发领先芯片的复杂性不断增加,减少晶圆边缘、斜面和背面的缺陷变得至关重要。因为单一的缺陷可能会在多个工艺和多芯片封装中产生昂贵的连锁反应。

这种情况由于混合键合等工艺的广泛应用而更加复杂,混合键合需要完美的表面。同时,在多芯片/Chiplet(小芯片)设计中对可靠性的重视也在增加,在这种情况下,潜在的缺陷可能会导致多个Chiplet报废。找到缺陷的根本原因,确保它不是系统性问题,并且不会降低所有晶圆的良率,这一过程可能会导致数月的延迟。

在300mm晶圆边缘生产高良率芯片的难度极大,原因有很多,包括晶圆均匀性、工艺变化以及诸如薄膜应力等多层效应。保持晶圆整体的均匀性尤其具有挑战性。每片晶圆可能需要进行多达1000个工艺步骤,包括图案化、沉积、蚀刻、CMP(化学机械抛光)和电镀。虽然静电卡盘和晶圆边缘环专门设计用于提高工艺均匀性,但边缘条件仍然容易下降。干法和湿法工艺都可以使用,但湿法蚀刻也可能会损坏晶圆边缘——这是3D NAND工艺中的一个关键问题,3D NAND工艺正在迅速向混合键合推进。

最糟糕的情况是,边缘缺陷可能是晶圆破损的罪魁祸首,而这代价特别昂贵。布鲁克(Bruker)公司英国站点经理John Wall表示:“边缘缺陷可能是晶圆破损的主要原因,这会中断生产线,导致成本非常高。”这些成本与产品损失、清洁工艺室的时间有关,最关键的是找到破损的根本原因。

“晶圆破损通常发生在激进的工艺步骤期间,如快速热退火(RTA)或CMP。”Wall表示,“但导致破损的缺陷,作为破损的前兆,可以在之前的许多不同工艺步骤中形成。例如,通过处理影响晶圆边缘的错误。如果晶圆上不存在这些缺陷,那么晶圆在RTA或CMP过程中就不会破损。”

提高晶圆边缘芯片的良率可以带来显著的回报,具体取决于设备类型和良率。“晶圆边缘仍有很大的良率潜力,”DR Yield的CEO Dieter Rathei说道。根据工艺的不同,提升边缘良率的重点可能需要工艺、产品和良率工程师团队的资源,这可能成本高昂。“提升良率潜力很大,但从经济角度来看,问题是获得最后那一点良率提升的努力是否划算。”

晶圆边缘缺陷带来高昂成本风险

晶圆边缘的缺陷包括颗粒、碎裂、划痕、薄膜剥落等。在产品开发阶段,表面缺陷以及硅和外延层中的表体缺陷(如晶格空隙和滑移)必须及早发现,以便在大规模生产中及时解决。光学方法通常使用红外散射法检测隐藏的缺陷,如针孔或气泡。X射线衍射成像(XRDI)可以识别Si/SiGe超晶格结构中的外延层位错,这些位错会影响鳍式场效应晶体管(FinFET)和全环绕栅极(GAA)晶体管的性能。电子束计量使用电压对比可以帮助识别临界尺寸(CD)和套刻工艺变化,这些问题会因为薄膜应力和晶圆弯曲而加剧。

特别是3D NAND堆叠,需要确保在将多个内存堆叠与逻辑外围晶圆键合之前,内存堆叠是良好的。“制造中人们使用了双重光刻与双重蚀刻(光刻-蚀刻,光刻-蚀刻),但设备中一个芯片与另一个芯片之间的最终电气错位是光刻的函数——同时也受到蚀刻图案、薄膜均匀性和CMP均匀性的影响,” PDF Solutions的技术专家Tomasz Brozek说道。由于弯曲或蚀刻和CMP工艺不均匀性等问题,晶圆边缘区域可能存在最大的变异。

“通过使用面向检测设计的测试结构和具有电压对比功能的电子束探针,可以电学测量这些结构,可以对结构进行电气测量,以识别晶圆上排列(覆盖)和临界尺寸线宽的最小变化。”Brozek说,“由于你希望将良好的芯片叠加在良好的芯片上,因此在堆叠芯片之前需要了解它们的电学特性。而这已经在进行。”

在3D NAND制造中还有其他的变异问题,堆叠数百层薄膜也增加了损坏晶圆边缘的机会。特别是非常长时间的湿法蚀刻会在晶圆边缘产生残留物、提高粗糙度和损伤,导致材料剥落、漂移到其他区域并产生缺陷,从而导致半导体器件失效。

在采用先进封装的2.5D和3.5D配置中,堆叠芯片的过渡对控制晶圆边缘轮廓的CMP步骤提出了严格要求。在这里,边缘滚落必须在每片晶圆之间保持一致,因为边缘轮廓对键合质量尤为重要。

初始晶圆

晶圆制造商和芯片制造商使用无图案晶圆检测工具来确定所谓的裸硅、外延晶圆、SOI(绝缘体上硅)、硅上氮化镓(GaN)以及碳化硅(SiC)晶圆的质量。Onto Innovation的产品营销高级经理Burhan Ali表示:“不同基板类型的缺陷检测要求各不相同。例如,在硅晶圆中,用于领先节点的外延晶圆的检测要求具有更严格的工艺控制,最小缺陷尺寸要求已达到纳米级别。”

无图案晶圆检测通常使用基于光学图像或激光散射的方法,这些方法可以有效地捕捉晶圆正面和背面的表面缺陷,如颗粒、划痕和坑洞。符合或超过工艺规格的裸晶圆会被运送到晶圆厂,晶圆厂通常使用相同的检测方法进行进货质量检查。

无图案检测也在晶圆厂内部进行,用于监控工艺工具,检查生产线中的颗粒或其他污染物(所谓的“空白晶圆”)。此外,基板制造商还使用红外散射测量或X射线衍射成像等技术检查表体缺陷,以穿透晶圆表面,检测诸如针孔或气泡等缺陷。

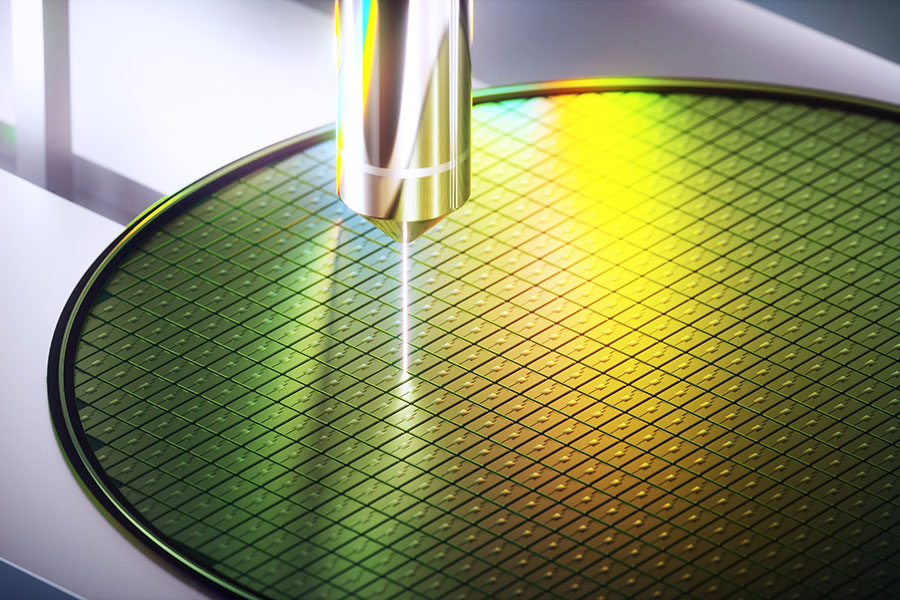

检测晶圆的正面、背面和斜面

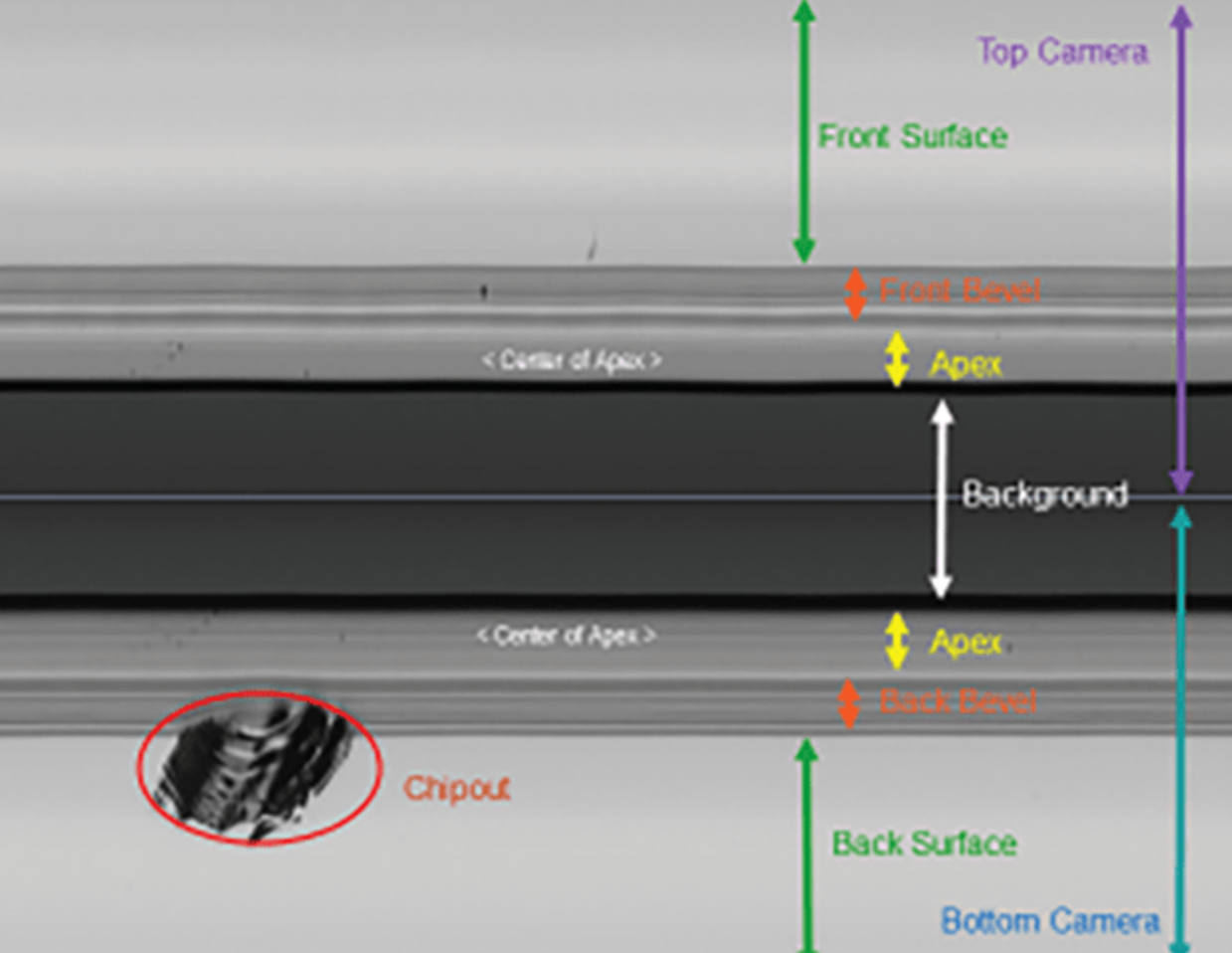

图案化晶圆检测平台用于检测晶圆的正面、背面和斜面上的缺陷(见图1)。Ali表示:“对裸晶圆和图案化晶圆的倒角检测通常使用明场和/或暗场照明,利用多个摄像头覆盖整个倒角区域,以确保晶圆的顶部倒角、顶点和底部倒角没有盲区。”“旋转晶圆以获取整个倒角的图像,然后对缺陷进行分类。”

图1:晶圆边缘图像显示了倒角、顶点和体硅区域,以及背面缺陷。来源:Onto Innovation

在线光学检测通常用于检测工艺中的异常情况,并区分良品区域与缺陷区域。Ali表示:“一些较为流行的方法包括金模比较、模对模比较和基于CAD的检测。”

自动缺陷分类(ADC)通常采用机器学习算法来提高分类的准确性和速度。先进的ADC应用于所有表面,包括背面、正面和斜面——包括缺口。Ali说:“客户希望更快地得出结果,以优化他们的工艺并最大限度减少审核时间。”晶圆缺口用于在工艺工具中精确定位晶圆。但晶圆边缘的凹痕进一步揭示了硅晶格的晶体取向(111、100或110取向),设备工程师可以选择这些取向来优化设备的电气性能。

晶圆背面最常见的缺陷之一是热点。在深紫外线或极紫外线光刻过程中,背面颗粒可能会改变图案化时的焦深。此外,背面缺陷可能导致蚀刻和离子注入过程中工艺的不均匀性。在极端情况下,当晶圆片被静电卡盘拉平时,背面颗粒也会导致晶圆片破裂。

晶圆倒角处理也可能与颗粒问题有关。DR Yield的Rathei表示:“晶圆倒角有各种处理方式,甚至可能有来自背面的颗粒沿着边缘移动。”例如,倒角效果来自EBR(边缘去除剂),而且由于边缘的断裂会导致光刻图案缺陷,因此光刻覆盖和CD误差会更为显著。

当背面颗粒移动到正面设备时,无论是在处理、加工或在前开式晶圆传送盒(FOUP)中,它们可能会成为致命缺陷。边珠去除过程去除的是湿化学过程中形成的光刻胶或显影剂的边缘珠。光刻跟踪系统中的其他过程包括在晶圆过渡到下一个工艺步骤(通常是等离子体或反应离子蚀刻室)之前,对晶圆进行背面清洗和干燥。

在先进封装中,成品芯片的电性能变化变得尤为重要。在这种封装中,相同类型的Chiplet(如HBM4)会被配对并堆叠,异质Chiplet(如SRAM和处理器)也会堆叠,或者像HBM和处理器这样的异质芯片会进行横向互连。

由于许多晶圆边缘缺陷可能是由于工艺室中的晶圆中心定位误差造成的,因此每次都必须使用传感器来确保晶圆在其夹具上居中。Nordson Test & Measurement的WaferSense高级项目经理Vidya Vijay表示:“例如,Teach传感器可以帮助确定晶圆在蚀刻室中的放置是否居中。”她进一步指出,“精确的居中至关重要。任何偏离中心的位置都可能导致下游严重的良率问题。因此,它可以训练机器人和末端执行器将晶圆放置在中心。”

对于沉积工艺,使用电容传感器来确保沉积室中喷头和台座之间的间隙完全一致,每个300mm的工具通常有多个沉积室。Vijay表示:“这个间隙是一个非常关键的工艺标准,因为沉积厚度和均匀性的可重复性和再现性依赖于每片晶圆上保持一致的间隙。”

晶格缺陷

随着向3D结构的过渡,如FinFET、GAAFET和多层超晶格结构,外延层的质量监测变得至关重要。

Bruker的Wall表示:“对于微小缺陷,外延生长后的检测极为重要。”在外延层生长过程中(CVD工艺)形成的微小缺陷可能导致晶格不匹配、位错和滑移。这些是晶体缺陷,如果外延层生长失控,就会形成这些缺陷。

他还表示:“在材料中,特别是在硅/硅锗超晶格中,可能会出现应变的松弛或释放。”“XRDI技术对这些类型的缺陷非常敏感。我们通过晶圆中的晶面对准衍射平面。即使硅晶格中缺少一个原子,也会扭曲晶体晶格,产生一个强的应变场,这种应变场可能扩展到数十微米。如果你将其放大,滑移是指整个晶体平面移动并释放了张力。”

关键是捕捉超晶格结构中应变松弛的开始。Wall说:“XRDI对松弛的开始非常敏感,因此我们能够看到某些情况下位错的形成,并且具有良好的对比度。它提供了一种新的视角,使我们对松弛的开始更为敏感,因为在开始阶段,你的工艺本质上已经失控。”

先进封装的应对策略

混合键合需要严格的工艺控制——特别是在键合过程之前,因为任何存在于键合晶圆表面的颗粒都可能导致形成气孔。Onto Innovation的Ali表示:“随着铜(Cu)垫的关键尺寸和间距缩小,越来越小的颗粒可能会导致严重影响良率的气孔。”

在晶圆对晶圆键合的情况下,这是当前最常用的混合键合方法,需要更高灵敏度的光学检测工具来检测这些更小的缺陷。键合后还需要进行额外的检测步骤,以确保在介电-介电和Cu/Cu表面之间的键合区域没有气孔。

另一种在先进封装中使用越来越多的的光学技术是白光干涉仪(WLI),它是光学轮廓仪的一个子集设备。WLI具有非破坏性,视野宽广,达到2毫米,同时提供足够的横向和纵向分辨率来表征晶圆边缘滚落。

Bruker技术与应用开发总监Samuel Lesko表示:“滚落在晶圆的键合效果中扮演着重要角色。例如,这些晶圆通常经历了多个CMP步骤,因此跟踪晶圆的拓扑结构——它的下降速度和下降长度非常重要。光学轮廓仪在垂直方向上具有极高的纳米级灵敏度,这有助于在键合前作为质量控制在不同角度测量滚落。”

Lesko补充说,白光干涉仪和原子力显微镜(AFM)在表征CMP工艺中各有其作用,其中铜的抛光速度会比介电材料快,从而导致一些铜碟形。这个碟形腔必须在晶圆上非常均匀,以确保所有铜连接在退火时都能完成。

结论

为了最大化晶圆边缘的芯片良率,晶圆厂采用了多种计量和检测方法,并辅以机器学习算法以提供更快的结果。混合键合的应用对晶圆边缘性质提出了新的要求,必须满足这些要求才能实现高良率的晶圆对晶圆键合。(校对/孙乐)

参考

Ali,“裸晶圆片之谜:检测先进节点的背面、边缘和缺口缺陷”,2023年12月12日,https://semiengineering.com/a-bare-wafer-mystery-inspecting-for-back-edge-and-notch-defects-in-advanced-nodes/

本文编译来源:https://semiengineering.com/defect-challenges-grow-at-the-wafer-edge/

作者:LAURA PETERS